Modul I

Gerbang Logika Dasar, Monostable Multivibrator

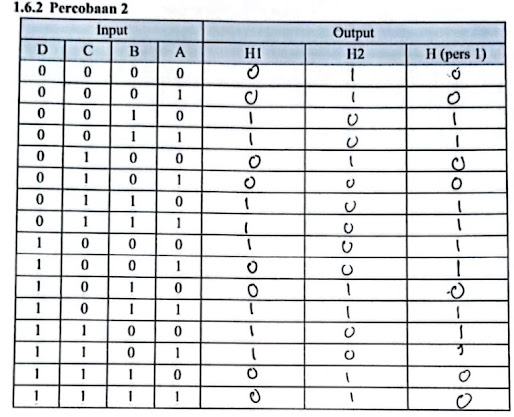

PERCOBAAN 2

DAFTAR ISI

3. Gambar Rangkaian

4. Prinsip Kerja

1. Jurnal [kembali]

2. Hardware [kembali]

- Panel DL 2203C

- Panel DL 2203D

- Panel DL 2203S

Gerbang Logika XOR ( IC 4030)

Gerbang logika XOR adalah singkatan dari EXclusive OR gate yang outputnya hanya akan bernilai logika 1 jika salah satu input X atau Y dalam keadaan bernilai logika 1, ketika semua inputnya dalam keadaan logika 0 atau dalam keadaan logika 1 maka output akan tetap logika 0.

NAND GATE

ketika inputnya ada yang 0 maka akan menghasilkan output 1. tapi ketika ada input yang berlogika 1

maka outputnya menjadi 0

AND GATE

ketika inputnya sama-sama 1 maka akan menghasilkan output 1. tapi ketika ada input yang berlogika 0

maka outputnya menjadi 0

Gerbang Logika OR (IC 7432)

4. Prinsip Kerja [kembali]

Gerbang NAND merupakan kombinasi dari gerbang AND dengan gerbang NOT dimana keluaran gerbang AND dihubungkan ke saluran masukan dari gerbang NOT. Karena keluaran dari gerbang AND di”NOT”kan maka prinsip kerja dari gerbang NAND merupakan kebalikan dari gerbang AND. Outputnya merupakan komplemen atau kebalikan dari gerbang AND, yakni memberikan keadaan level logic 0 pada outputnya jika dan hanya jika keadaan semua inputnya berlogika 1. Sama halnya dengan NAND Gate, gerbang NOR merupakan kombinasi dari gerbang OR dengan gerbang NOT dimana keluaran gerbang OR dihubungkan ke saluran masukan dari gerbang NOT. Karena keluaran dari gerbang OR di”NOT”kan maka prinsip kerja dari gerbang NOR merupakan kebalikan dari gerbang OR. Outputnya merupakan komplemen atau kebalikan dari gerbang OR, yakni memberikan keadaan level logic 0 pada outputnya jika salah satu atau lebih inputnya berlogika 1. EX-OR singkatan dari Exclusive OR dimana jika input berlogic sama maka output akan berlogic 0 dan sebaliknya jika input berlogic beda maka output akan berlogic 1. EX-NOR gate adalah kebalikan dari EX-OR gate dimana jika input berlogic sama maka output akan berlogic 1 dan sebaliknya jika input berlogic beda maka output akan berlogic 0.

5. Video Praktikum [kembali]6. Analisa [kembali]

1]. Jelaskan bagaimana mendapatkan persamaan H1 dan H2

Dengan menggunakan menggunakan Peta Karnough dan Aljabar Boolean terhadap fungsi yang telah diberikan dan fungsi tersebut disederhanakan dengan sifat-sifat pada boolean :

= AB`C`D + ABC`D + ABD` + A`BD` + A`B`C`D +A`B`CD + AB`CD

= AC'D(B' + B) + BD'(A + A') + A'B'D(C+C') + AB'CD

= BD' + A'B'D + AD(B'C+C')

= BD' +A'B'D + AD(B' +C')

= BD' +A'B'D + ADB' + ADC'

= BD' + B'D + ADC'

2]. Analisa dan bandingkan H1, H2 dan H pers

Pada Jurnal terlihat bahwa nilai H1 dan H2 bernilai saling berlawanan. dimana ketika logika H1 nya 0

maka logika dari H2 nya adalah 1. Hal ini karena inputan dari rangkaian berbeda meskipun rangkaiannya bergerbang logika yang sama. tapi ada ketidak sesuaian output ketika diberi

input tertentu. hal ini mungkin terjadi karena pemilihan komponennya yang tidak sesuai dengan

yang seharusnya atau kesalahan penghubungan kaki-kaki gerbang logika dengan inputannya

7. Link Download [kembali]

Datasheet NAND gate Link

Datasheet NOR gate Link

Datasheet XOR gate Link

Datasheet XNOR gate Link

Dataheet AND gate Link

Datasheet OR gate Link

Tidak ada komentar:

Posting Komentar