Modul II

FLIP FLIP

PERCOBAAN 1 JK flip flop dan D flip flop

DAFTAR ISI

3. Gambar Rangkaian

4. Prinsip Kerja

1. Jurnal [kembali]

2. Hardware [kembali]

|

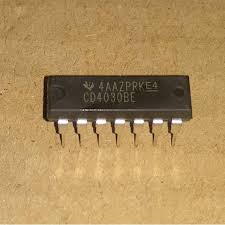

| Gambar 1.1 Module D`Lorenzo |

JK Flip Flop

D Flip Flop

3. Gambar Rangkaian [kembali]4. Prinsip Kerja [kembali]

D Flip Flop

Prinsip kerja dari rangkaian Data flip-flop dengan clock diatas adalahsebagai berikut.

Apabila input clock berlogika 1 “High” maka input pada jalur data akan di teruskan ke rangkaian RS flip flop, dimana pada saat input jalur Data 1 “High” maka kondisi tersebut adalah Set Q menjadi 1 “High” dan pada saat jalur Data diberikan input 0 “Low” maka kondisi yang terjadi adala Reset Q menjadi 0 “Low”.

Kemudian Pada saat input Clock berlogika rendah maka data output pada jalur Q akan ditahan (memori 1 bit) walaupun logika pada jalur input Data berubah. Kondisi inilah yang disebut sebagai dasar dari memor 1 bit.

J-K Flip Flop

JK Flip Flop adalah salah satu macam Flip Flop yang paling banyak diguankan dalam praktik.

Pada Flip Flop ini terdapat 3 buah input yaitu J, K dan CL, J dan K berfungsi sebagai pengendali ,

jika J = 0 dan K = 0 maka output Q akan tetap seperti keadaan semula walaupun input CL berubah-ubah.

jika J = 1 dan K = 0 , maka output Q akan di set (1) pada saat pulsa CL input bergerak dari 1 ke 0.

Jika J = 0 dan K = 1 maka output Q akan reset (0) pada saat pulsa CL input bergerak dari 1 ke 0.

Tetapi jika J = 1 dan K = 1 maka JK FlipFlop akan berfungsi sebagai T Flip Flop yaitu output akan berubah Jika CL bergerak dari 1 ke 0 . Hal ini bisa dikatakan Toggle.

Prinsip kerja dari rangkaian Data flip-flop dengan clock diatas adalahsebagai berikut.

Apabila input clock berlogika 1 “High” maka input pada jalur data akan di teruskan ke rangkaian RS flip flop, dimana pada saat input jalur Data 1 “High” maka kondisi tersebut adalah Set Q menjadi 1 “High” dan pada saat jalur Data diberikan input 0 “Low” maka kondisi yang terjadi adala Reset Q menjadi 0 “Low”.

Kemudian Pada saat input Clock berlogika rendah maka data output pada jalur Q akan ditahan (memori 1 bit) walaupun logika pada jalur input Data berubah. Kondisi inilah yang disebut sebagai dasar dari memor 1 bit.

J-K Flip Flop

JK Flip Flop adalah salah satu macam Flip Flop yang paling banyak diguankan dalam praktik.

5. Video Praktikum [kembali]

1. Bagaimana jika B0 dan B1 sama-sama diberi logika '0',apa yang terjadi pada rangkaian?

--->Rangkaian akan berada pada kondisi larangan,karena B0 dan B1 terhubung ke kaki R dan S pada JKflip flop dan D flip flop. dimana ketika input berlogika '0' maka yang masuk ke RS adalah kebalikannya sehingga outputnya menjadi '1','1'. dan ini bisa merusak alat. sesuai dengan prinsip RS flip flop

2. Bagaimana jika B3 diputuskan/tidak dihubungkan pada rangkaian,apa yang terjadi pada rangkaian?

--->J dan K tidak memberi pengaruh terhadap output sehingga outputnya hanya bergantung kepada RS sehingga rangkaian menjadi RS flip flop.

3. Jelaskan apa yang dimaksud dengan kondisi Toogle,Kondisi not change dan kondisi terlarang pada flip flop?

--->Toogle : Kondisi dimana nilai dari output berubah-ubah terus menerus ketika diberi clock.

Not Change : adalah kondisi suatu output/input sama dengan sebelumnya ketika kita ubah suatu nilai lainnya.

Larangan : Kondisi yang tidak boleh ada pada rangkaian flip flop dan perlu dihindari karena bisa merusak komponen dari rangkaian. dimana pada RS flip flop sama-sama berlogika '1' '1'

7. Link Download [kembali]

Datasheet kapasitor Link

Datasheet resistor Link

Datasheet multivibrator Link

Datasheet potensiometer Link

Datasheet NAND gate Link

Datasheet NOR gate Link

Datasheet XOR gate Link

Datasheet XNOR gate Link

Dataheet AND gate Link

Datasheet OR gate Link

Tidak ada komentar:

Posting Komentar