Modul II

FLIP FLOP

PERCOBAAN 2

DAFTAR ISI

3. Gambar Rangkaian

4. Prinsip Kerja

1. Jurnal [kembali]

2. Hardware [kembali]

|

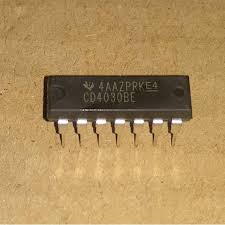

| Gambar 1.1 Module D`Lorenzo |

JK Flip Flop

3. Gambar Rangkaian [kembali]

4. Prinsip Kerja [kembali]

T Flip-flop merupakan rangkaian flip-flop yang telah di buat dengan menggunakan flip-flop J-K yang kedua inputnya dihubungkan menjadi satu maka akan diperoleh flip-flop yang memiliki watak membalik output sebelumnya jika inputannya tinggi dan outputnya akan tetap jika inputnya rendah.

4. Analisa [kembali]

Percobaan 2

1. Apa yang terjadi jika B1 diganti dengan Clock?

---> output dari T flip flop akan selalu bernilai '1' ketika diberi clock dan ketika B0 diganti ke '0' maka output Q nya akan toogle dimana akan '0' sebentar kemudian berubah menjadi '1'

2. Bandingkan hasil percobaan dengan teori

---> percobaan 2 memiliki hasil yang sama antara teori(proteus) dengan yang dilakukan ketika praktikum secara langsung dan sesuai dengan tabel kebenaran untuk T flip flop

3. Apa fungsi masing-masing flip flop yang digunakan?

---> Q sebagai output dari flip flop kaki S

Q' sebagai output dari flip flop kaki R

S sebagai set nilai Q yang induk pengubah utama Q

R sebagai set nilai Q' yang induk pengubah utama Q'

J dan K sebagai pengubah nilai jika S dan R berlogika '0'

Clock yang mentrigger pengubah nilai sehingga outputnya akan berubah-ubah ketika diberi clock pada kondisi tertentu

5. Link Download [kembali]

Datasheet kapasitor Link

Datasheet resistor Link

Datasheet multivibrator Link

Datasheet potensiometer Link

Datasheet NAND gate Link

Datasheet NOR gate Link

Datasheet XOR gate Link

Datasheet XNOR gate Link

Dataheet AND gate Link

Datasheet OR gate Link

Tidak ada komentar:

Posting Komentar