Modul III

COUNTER

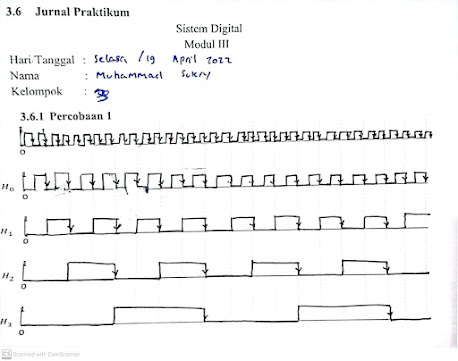

PERCOBAAN 1 Asynchronus Binary Counter 4 bit dengan JK Flip Flop

1. Jurnal [kembali]

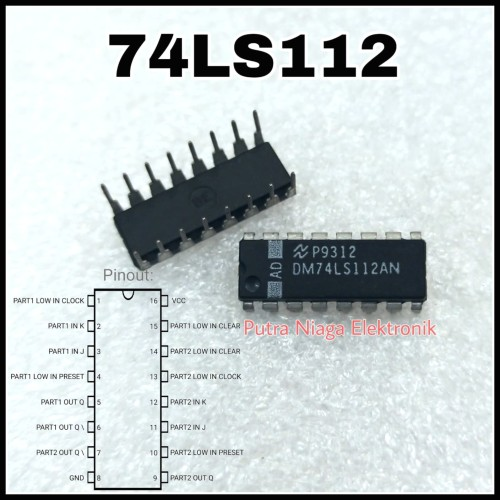

JK Flip Flop

3. Gambar Rangkaian [kembali]TABEL 74LS90

Pada IC 74LS90,kaki CKA merupakan inputan A berupa clock yang berhungsi sebagai pengatur output dari Q0 sedangkan kaki CKB merupakan inputan B berupa Clock yang berfungsi sebagai pengatur output dari Q1,Q2,dan Q3.

pada percobaan 2 ini,rangkaian yang digunakan adalah rangkaian Asyncronus sehingga CKB menerima input dari output CKA sehingga nilai CKB bergantung pada nilai CKA pada 74LS90

sedangkan R0 merupakan kaki reset dan R9 sebagai kaki set,kedua kaki inilah yang mempengaruhi perubahan pada output Q sehingga nilai nya bervariasi sesuai dengan tabel diatas.

TABEL 7493

Begitu Pula pada IC 7439,kaki CKA merupakan inputan A berupa clock yang berhungsi sebagai pengatur output dari Q0 sedangkan kaki CKB merupakan inputan B berupa Clock yang berfungsi sebagai pengatur output dari Q1,Q2,dan Q3.

pada percobaan 2 ini,rangkaian yang digunakan adalah rangkaian Asyncronus sehingga CKB menerima input dari output CKA sehingga nilai CKB bergantung pada nilai CKA pada 74LS90

Jawab:

Pada Percobaan 1 yang menggunakan JK Flip Flop kondisi Toogle maka didapatkan bahwa rangkaian ini merupakan counter up/ hal ini dikarenakan outputnya naik dari 0 hingga 15 secara bertahap/sequential

2. Analisa Output Percobaan berdasarkan sinyal output JK flip flop kedua dan ketiga

Jawab:

Pada JK Flip flop,nilai outputnya tergantung pada inputan yang diberikan,dimana pada percobaan ini JK flip flop kedua menerima input dari JK flip flop yang pertama begitu seterusnya. output JK akan berubah-ubah ketika clock aktif dan JK dalam kondisi toogle. JK kedua harus menunggu output dari JK pertama dan JK 3 harus menunggu dari JK 2 untuk memicu clock pada JK 3. hal inilah yang menyebabkan rangkaian disebut counter Asynchronus

Tidak ada komentar:

Posting Komentar