Modul III

COUNTER

PERCOBAAN 3 Synchronus Binary Counter dengan IC 74193 dan 74192

1. Jurnal [kembali]

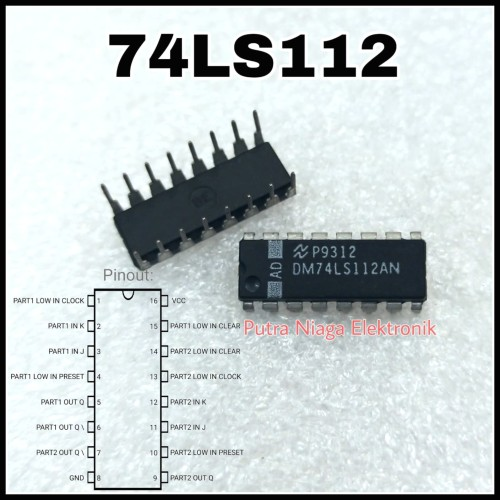

JK Flip Flop

3. Gambar Rangkaian [kembali]4. Prinsip Kerja [kembali]

Bersifat Counter UP ketika diberi clock pada Kaki UP dan counter down ketika diberi clock pada kaki DN dan mereset nilai jika MR nya 1. serta mematikan kondisi counter ketika diberi logika 0 pada kaki PL

Bersifat Counter UP ketika diberi clock pada Kaki UP dan counter down ketika diberi clock pada kaki DN dan mereset nilai jika MR nya 1. serta mematikan kondisi counter ketika diberi logika 0 pada kaki PL

keduanya bekerja bersamaan sehingga disebut counter synchronus dan batasnya berbeda ada yang sampai 15 dan ada yang sampai 9 sesuai dengan spesifikasi IC nya

1. Analisa Output percobaan berdasarkan IC yang dipakaiJawab:

Berdasarkan percobaan yang dilakukan,didapatkan bahwa rangkaiannnya adalah rangkaian syncronus karena keduanya bekerja dalam waktu yang bersamaan. outputnya berupa counter up tapi karena perbedaan IC yang dgunakan membuat batasan nilai counter nya berbeda

2. Analisa hasil percobaan pada kondisi 3 dan 4

Jawab:

Pada Kondisi 3 hal yang terjadi adalah on tapi dia tidak mengcounter. hal ini disebabkan tidak adanya clock yang mengalir ke kaki UP atau DN sebagai tanda IC itu mencounter sedangkan pada kondisi 4 hal yang terjadi adalah counter up karena ada clock yang terhubung ke kaki UP sebagai penanda ia menjadi counter up

3. Apa pengaruh Gerbang OR pada rangkaian

Jawab:

Sebagai Inputan Clock sekaligus input saklar jadi ketika switch untuk counter up diputus dan counter down terhubung maka ketika clock IC akan langsung menjadi counter down begitu pula sebaliknya tapi ketika keduanya switch on maka tidak terjadi proses counter

7. Link Download [kembali]

Datasheet kapasitor Link

Datasheet resistor Link

Datasheet multivibrator Link

Datasheet potensiometer Link

Datasheet NAND gate Link

Datasheet NOR gate Link

Datasheet XOR gate Link

Datasheet XNOR gate Link

Dataheet AND gate Link

Datasheet OR gate Link

Tidak ada komentar:

Posting Komentar